### Muen - An x86/64 Separation Kernel for High Assurance

Reto Buerki Adrian-Ken Rueegsegger

August 29, 2013

University of Applied Sciences Rapperswil (HSR), Switzerland

## Abstract

Computer systems are used to store and protect highly sensitive data. At the same time the resources and determination of attackers have increased significantly. Therefore, systems capable of safeguarding critical information must conform to rigorous quality standards to establish trust in the correct functioning.

Attaining high assurance for today's monolithic operating systems is exceptionally hard since they tend to be large and include complex functionality. This fact is highlighted by regular security updates provided by operating system vendors. Thus, they are a weak foundation for building secure systems.

In contrast, microkernels can be well suited as a basis for systems with strict demands on robustness. They are by definition small, which is a precondition for rigorous verification of correctness. Additionally, they lend themselves to the construction of component-based systems where the incorrect behavior of one partition does not impact the whole system.

A separation kernel (SK) is a specialized microkernel that provides an execution environment for multiple components that can only communicate according to a given policy and are otherwise isolated from each other. Hence, the isolation also includes the limitation of potential side- and covert channels. SKs are generally more static and smaller than dynamic microkernels, which minimizes the possibility of kernel failure and should ease the application of formal verification techniques.

Recent addition of advanced hardware virtualization support for the Intel x86 architecture has the potential of greatly simplifying the implementation of a separation kernel which can support complex systems.

This thesis presents a design of a separation kernel for the Intel x86 architecture using the latest Intel hardware features. An open-source prototype written in SPARK demonstrates the viability of the envisioned concept and the application of SPARK's proof capabilities increases the assurance of the correctness of the implementation.

## Acknowledgments

Foremost, we would like to express our sincere gratitude to our advisor Prof. Dr. Andreas Steffen for the continuous support in the course of our studies and for the guidance in writing this master thesis. His help and generosity allowed us to work in such an interesting field of research.

Many thanks also to our colleagues and friends at secure Security Networks AG in Germany, Alexander Senier, Robert Dorn and Stefan Berghofer for their tremendous assistance not only during this thesis, but also during the many projects we have realized together. We were able to learn a lot and without their support and immense knowledge in the area of high-security platforms we would not have been able to implement the Muen kernel in such short time.

We thank Prof. Dr. Endre Bangerter from the University of Applied Sciences in Bern for being our expert and reviewer. Thanks also to Daniel Bigelow for proofreading the report.

Last but not least, many thanks to our families and friends for their support and understanding throughout the writing of this master thesis.

## Contents

|   | bstra                                                                       | ict                                                                                                                                                                                                                                                                                                                                |   | iii                                                  |  |

|---|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------|--|

| A | cknov                                                                       | wledgments                                                                                                                                                                                                                                                                                                                         |   | v                                                    |  |

| 1 | <b>Intr</b><br>1.1<br>1.2<br>1.3                                            | aroduction         Notation         Related Literature         Provenance of Name                                                                                                                                                                                                                                                  |   |                                                      |  |

| 2 | <b>Bac</b> 2.1 2.2                                                          | kground         SPARK         2.1.1       Design Rationale         2.1.2       Example         2.1.3       SPARK 2014         1ntel x86       Architecture         2.2.1       Processor         2.2.2       Memory Management         2.2.3       Exceptions and Interrupts         2.2.4       Programmable Interrupt Controller |   | . 4<br>. 5<br>. 5<br>. 5<br>. 5<br>. 7<br>. 9        |  |

|   | <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol> | 2.2.4       Frogrammable Interrupt Controller         2.2.5       Chipset connectivity         Virtualization                                                                                                                                                                                                                      |   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

| 3 | <b>Des</b><br>3.1<br>3.2<br>3.3                                             | ign           Scope                                                                                                                                                                                                                                                                                                                | • | . 20<br>. 21<br>. 21                                 |  |

|          |     | 3.3.3          | Subject Profile                                       |

|----------|-----|----------------|-------------------------------------------------------|

|          | 3.4 | Archit         | ecture                                                |

|          |     | 3.4.1          | Subject Execution                                     |

|          |     | 3.4.2          | Policy                                                |

|          |     | 3.4.3          | Inter-Subject Communication                           |

|          |     | 3.4.4          | Exceptions                                            |

|          |     | 3.4.5          | Interrupts                                            |

|          |     | 3.4.6          | Multicore                                             |

|          |     | 3.4.7          | Scheduling                                            |

|          |     | 0.1.1          |                                                       |

| <b>4</b> | Imp | lement         | tation 31                                             |

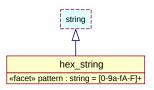

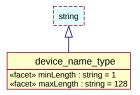

|          | 4.1 | Policy         | 31                                                    |

|          |     | 4.1.1          | Data Types                                            |

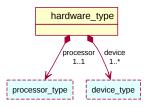

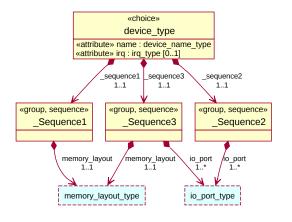

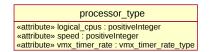

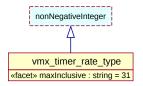

|          |     | 4.1.2          | Hardware                                              |

|          |     | 4.1.3          | Kernel                                                |

|          |     | 4.1.4          | Binaries                                              |

|          |     | 4.1.5          | Subjects                                              |

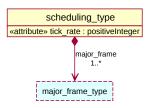

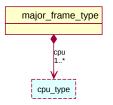

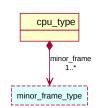

|          |     | 4.1.6          | Scheduling                                            |

|          | 4.2 | -              | 'ootprint Runtime   41                                |

|          | 4.3 | Subjec         |                                                       |

|          | 1.0 | 4.3.1          | Specification $42$                                    |

|          |     | 4.3.2          | State                                                 |

|          | 4.4 |                | L                                                     |

|          | 4.4 | 4.4.1          | Init $44$                                             |

|          |     | 4.4.1          | Multicore Support                                     |

|          |     | 4.4.2<br>4.4.3 | Scheduling         40           47                    |

|          |     | 4.4.3          | 0                                                     |

|          |     |                | 1 5                                                   |

|          |     | 4.4.5          | Traps         49           D         I         50     |

|          |     | 4.4.6          | External Interrupts                                   |

|          |     | 4.4.7          | Exceptions and Software-generated Interrupts          |

|          |     | 4.4.8          | Events                                                |

|          |     | 4.4.9          | Debug                                                 |

|          | 4.5 | Build .        |                                                       |

|          |     | 4.5.1          | Subject Binary Analysis       55                      |

|          |     | 4.5.2          | Policy Compilation                                    |

|          |     | 4.5.3          | Image Packaging                                       |

|          |     | 4.5.4          | Emulation                                             |

|          | 4.6 | -              | ple System                                            |

|          |     | 4.6.1          | Subjects                                              |

|          |     | 4.6.2          | Keyboard Handling                                     |

| _        |     |                |                                                       |

| 5        |     | lysis          | 63                                                    |

|          | 5.1 | -              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|          |     | 5.1.1          | VMX Controls                                          |

|          |     | 5.1.2          | System Resources                                      |

|          |     | 5.1.3          | Execution Environment                                 |

|          |     | 5.1.4          | Temporal Isolation                                    |

|          | 5.2 |                | nation Flow                                           |

|          |     | 5.2.1          | Shared Memory                                         |

|              |        | 5.2.2   | Events                                   | 70 |

|--------------|--------|---------|------------------------------------------|----|

|              |        | 5.2.3   | Traps                                    | 70 |

|              | 5.3    | Archit  | ecture Support                           | 71 |

|              |        | 5.3.1   | Kernel                                   | 71 |

|              |        | 5.3.2   | Subject                                  | 72 |

|              | 5.4    | Imple   | mentation Assurance                      | 72 |

|              |        | 5.4.1   | Lean Implementation                      | 72 |

|              |        | 5.4.2   | Small Size                               | 72 |

|              |        | 5.4.3   | Choice of Programming Language           | 73 |

|              |        | 5.4.4   | Tools                                    | 73 |

|              |        | 5.4.5   | Verifiability                            | 73 |

| 6            | Cor    | nclusio | n                                        | 75 |

|              | 6.1    | Contr   | ibutions                                 | 75 |

|              | 6.2    | Future  | e Work                                   | 75 |

|              |        | 6.2.1   | Covert/Side-Channel Analysis             | 76 |

|              |        | 6.2.2   | Linux Subject                            | 76 |

|              |        | 6.2.3   | Hardware Passthrough/PCIe Virtualization | 77 |

|              |        | 6.2.4   | APIC Virtualization                      | 77 |

|              |        | 6.2.5   | Policy Writer Support Tools              | 77 |

|              |        | 6.2.6   | Dynamic Resource Management              | 78 |

|              |        | 6.2.7   | Formal Verification                      | 78 |

| In           | dex    |         |                                          | 79 |

| B            | ibliod | graphy  |                                          | 83 |

| $\mathbf{D}$ | ισποέ  | srapity |                                          | 00 |

#### Bibliography

# List of Figures

| 1.1  | Muen in kanji                             | 2         |

|------|-------------------------------------------|-----------|

| 2.1  | Intel architecture                        | 6         |

| 2.2  | One-level address translation             | 8         |

| 2.3  | Local APICs and I/O APIC                  | 0         |

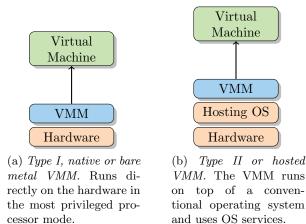

| 2.4  | VMM classification                        | 1         |

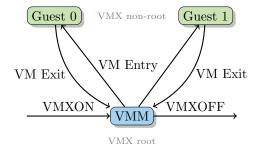

| 2.5  |                                           | 2         |

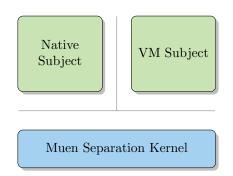

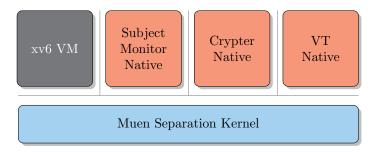

| 3.1  | Architecture overview                     | 23        |

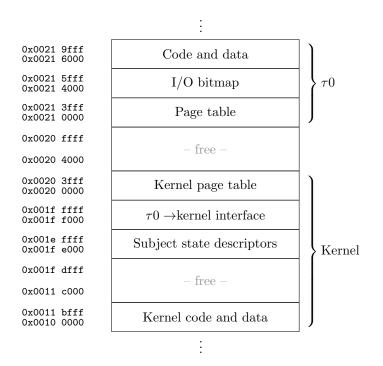

| 3.2  | Physical memory layout example            | 25        |

| 3.3  | Virtual memory layout of example subject  | 26        |

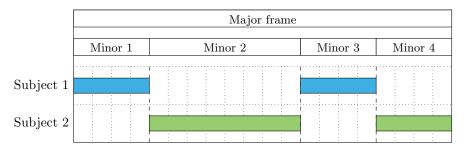

| 3.4  | Example major frame 2                     | 29        |

| 3.5  |                                           | 80        |

| 4.1  | Example memory layout on system init      | 15        |

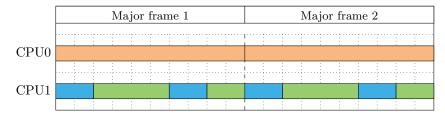

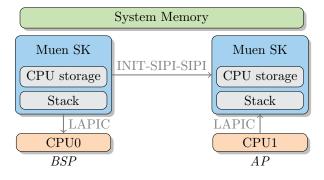

| 4.2  | Multicore architecture                    | 16        |

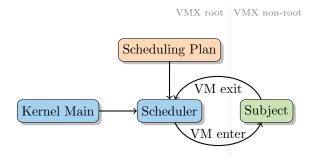

| 4.3  | Kernel scheduler                          | 18        |

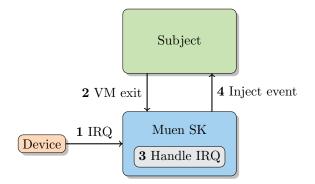

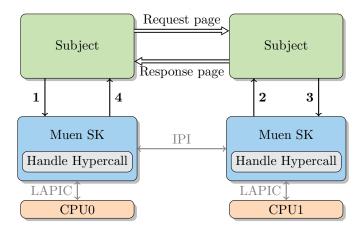

| 4.4  | External interrupt handling 5             | 51        |

| 4.5  | Inter-core events                         | 53        |

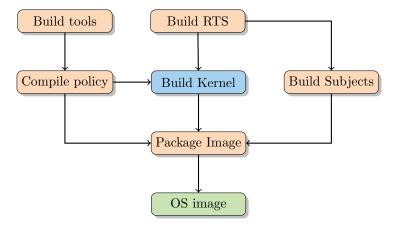

| 4.6  | Build process 5                           | <b>54</b> |

| 4.7  | From binary object to XML specification 5 | 55        |

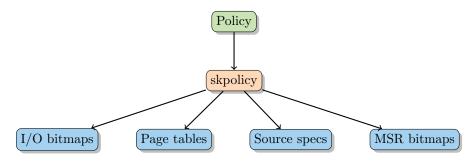

| 4.8  | Policy compilation                        | <b>56</b> |

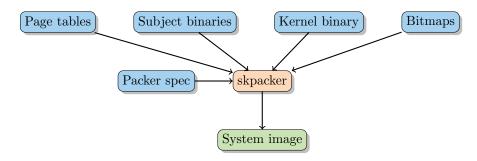

| 4.9  | System image packaging 5                  | 57        |

| 4.10 | Example system                            | 59        |

## List of Tables

| 5.1 | Subject profile VM exit comparison    | 64 |

|-----|---------------------------------------|----|

| 5.2 | Execution environment and VMCS fields | 66 |

| 5.3 | VMCS segment register fields          | 66 |

| 5.4 | VMCS control register fields          | 67 |

| 5.5 | SPARK kernel proof summary            | 73 |

|     |                                       |    |

## Listings

| 2.1  | SPARK example                            | 5  |

|------|------------------------------------------|----|

| 4.1  | Restriction pragmas                      | 41 |

| 4.2  | SPARK subject spec type                  | 42 |

| 4.3  | SPARK subject state type                 | 43 |

| 4.4  |                                          | 43 |

| 4.5  | SPARK null subject state constant        | 43 |

| 4.6  | SPARK null CPU registers constant        | 44 |

| 4.7  | System scheduling plan in XML            | 47 |

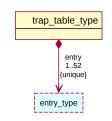

| 4.8  | Subject trap table                       | 49 |

| 4.9  | Trap table specification                 | 50 |

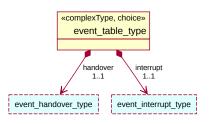

| 4.10 | Subject event table                      | 52 |

| 4.11 | Kernel debug statement                   | 53 |

| 4.12 | Example output of skpacker tool          | 58 |

| 4.13 | Subject device assignment                | 59 |

| 4.14 | Example system IRQ routing table         | 60 |

| 4.15 | Example system CPU0 vector routing table | 61 |

|      |                                          |    |

# Chapter 1 Introduction

As computer systems are entrusted with more and more sensitive and personal information, the need to effectively control access to the data becomes increasingly important. Recent revelations about very sophisticated and targeted attacks as well as broad, nation-wide surveillance programs seriously call the effectiveness of currently deployed security systems in question.

A common defense strategy is to compartmentalize information and its processing. An example would be the usage of a dedicated computer for Internet banking that is only connected to the Internet when needed. However, this approach does not scale well, since this would necessitate having a separate device for each task that should be performed in some form of isolation.

A separation kernel (SK) is a specialized microkernel which provides an execution environment for components that can only communicate according to a given policy and are otherwise isolated from each other. This isolation also includes the limitation of potential side- and covert channels. A SK can serve as a basis for the implementation of a component-based system.

Related problems can arise in cloud services, where multiple unaffiliated parties share the same physical machine but are to be separated from each other so as to not (involuntarily) share any data. Recent attacks [42] have demonstrated that current solutions do not provide the necessary degree of isolation. Since the adoption of virtualization, especially in the field of cloud computing, has rapidly increased in the past years, chip manufacturers such as Intel are extending their processors with advanced hardware virtualization features.

Another issue is the complexity associated with developing security systems that must exhibit very strong robustness and provide high assurance. Tools and methods such as formal verification exist, but are generally disregarded. A small code base results in better verifiability since the complexity of the software should be manageable and the effort needed for review is greatly reduced.

The SPARK programming language is used for the development of industrial high integrity projects. It provides the means to prove certain properties of the code and its track record [6] shows that it can be used to effectively implement real-world systems.

All these recent developments provide a good setting for the design and implementation of an open-source separation kernel. Using hardware virtualization features for component separation and leveraging Intel's latest processor features should allow to implement a small kernel suitable for formal verification. Using SPARK as the programming language greatly increases the confidence in the implementation since it eliminates complete categories of common programming errors, e.g. buffer overflows. Making the source code and technical documentation publicly available enables third-party review.

This document presents the design and implementation of the Muen separation kernel, which

was developed during the course of our master thesis.

#### 1.1 Notation

This section presents the notational conventions used throughout this document.

**Keywords** Important terms and concepts that are introduced for the first time are presented in *italic style*. Subsequent occurrences of the same term have no special formatting. The same style is also used to *emphasize* words in the text.

**Numbers** Regular numbers that have no leading special character are expressed as decimal values. Hexadecimal numbers such as memory addresses are explicitly preceded by 0x.

**Units** Storage units such as kilo-, mega- and gigabyte are designated by the common abbreviations KB, MB and GB.

**Tools and Procedures** References to subroutines and keywords of a programming language, as well as command line tools are formatted in **typewriter** style.

#### **1.2** Related Literature

Since the target hardware platform of the separation kernel is the Intel x86 architecture, its specification called "Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual" [17] is the main source of technical information concerning the hardware platform. The documents are commonly referred to by their short name *Intel SDM*.

The books are available online and updated by Intel on a regular basis. This can lead to changes in the document structure. The chapter and section citations given in this report refer to the Intel SDM revision 44, released in August 2012.

#### **1.3** Provenance of Name

*Muen* is Japanese and translates to "unrelated/without relation". It was chosen since it is a fitting allegory of the components isolated by the separation kernel. Figure 1.1 depicts the word in Japanese kanji characters<sup>1</sup>.

Figure 1.1: Muen in kanji

The root of the word Muen is "Mu" which denotes a negative: the absence of everything. It is a keyword in Chan and Zen Buddhism and also mentioned in the Jargon File [30].

<sup>&</sup>lt;sup>1</sup>The Unicode code points of the two characters are U+28961 U+32257.

# Chapter 2 Background

This chapter introduces technologies and concepts which are necessary for the understanding of the design and the realization of the Muen kernel. First we present SPARK, the programming language chosen for the implementation. After that, a short description of the Intel/PC architecture is given, followed by an introduction into virtualization. The concept of the separation kernel is presented and the main motivation and goals of this work is laid out. The chapter concludes with an overview of related projects.

#### 2.1 SPARK

SPARK is a precisely defined high-level programming language designed for implementing high integrity systems. It is based on Ada, which is itself a programming language with a strong focus on security and safety.

The SPARK language is a subset of Ada with additional features inserted as annotations in the form of Ada comments. Since compilers ignore comments and SPARK is a true subset of Ada, any correct SPARK program is a correct Ada program and can be compiled using existing Ada compilers. One such compiler is GNAT, which is part of the GNU compiler collection (GCC) [12].

However, since annotations are an integral part of SPARK, it would be misleading to simply consider SPARK a constrained version of Ada. SPARK should be viewed as a programming language in its own right. The following list summarizes the Ada restrictions imposed by SPARK:

- No access types (pointers)

- No recursion

- No exceptions

- No goto

- No anonymous and aliased types

- No functions with side-effects

- No dynamic array bounds

- No dynamic memory allocation

• No dynamic dispatching

Annotations are processed by SPARK tools. These tools perform static analysis of source code. The annotations allow the tools to do data and information flow analysis as well as prove the absence of runtime errors. This means that SPARK tools allow one to formally verify that a given program is free of errors such as division by zero, out-of-bounds array access etc. By using SPARK the following types of errors can be proven to be absent from the code:

- Incorrect indexing of arrays

- Overflows

- Division by zero

- Type range violations

- Memory exhaustion

- Dangling pointers

On top of these properties, the usage of pre-/post-conditions and assertions allow to prove additional functional properties. A proof of (partial<sup>1</sup>) correctness of SPARK programs is achievable. This allows one to formally show the correspondence of an implementation with a formal specification.

It is also interesting to note, that SPARK has support for tasking in the form of a language profile<sup>2</sup> called RavenSPARK [36].

SPARK is a mature technology and has garnered quite some interest since it has been successfully used in several industrial projects [6]. It is primarily employed in the field of avionics, space, medical systems and the defense industry.

#### 2.1.1 Design Rationale

The main driving factors behind the design of SPARK as stated by the language reference manual [35] are briefly described here:

#### Logical soundness

The language must not contain any ambiguities and must be formally defined.

#### Complexity of formal language definition

The language must be simple to specify formally.

#### Expressive power

The language must be expressive enough to implement complex systems.

#### Security

It must be possible to avoid entering error conditions or undefined state at runtime by static program analysis with a reasonable effort.

#### Verifiability

Program verification must be modular in order to be tractable for industrial scale projects.

#### Bounded space and time requirements

It must be possible to statically determine resource requirements.

$<sup>^1\</sup>mathrm{Termination}$  cannot be shown

$<sup>^{2}</sup>$ Restricted subset of the programming language

#### 2.1.2Example

2

3

$\mathbf{5}$

6

The following listing illustrates how annotations are used to specify the contract of a subprogram.

```

type Color_Type is (Red, Green, Blue);

procedure Exchange (X, Y: in out Color_Type);

4

-# derives X from Y &

Y from X;

--#

--# post X = Y\sim and Y = X\sim;

```

#### Listing 2.1: SPARK example

The declaration of the Exchange procedure states that it has two parameters X and Y which are of mode in out. This means that the values of both parameters are imported (in) and exported (out).

Since the specification does not contain a global annotation, no other state (i.e. global variables) is accessed and the procedure is therefore free of side-effects. The derives annotation states the data flow: the value of X is derived from Y and vice versa.

Lastly, the postcondition specifies the values of X and Y after the procedure has been executed. An identifier decorated with the tilde symbol  $(\sim)$  indicates the initial imported value of the variable. Thus the **post** annotation states that X will be assigned the initial value of Y and likewise for Y.

It should be noted that the Color\_Type is a *distinct* enumeration type which *cannot* be mixed with other types.

An in-depth discussion of the SPARK programming language can be found in [4].

#### **SPARK 2014** 2.1.3

At the time of writing<sup>3</sup>, the SPARK language is undergoing a major transformation. The goal is to extend the subset of Ada included in SPARK and to make use of the new Ada 2012 features [3]. The use of Ada 2012 aspects will replace the SPARK annotation comments. The official SPARK 2014 release is expected in the first quarter of 2014 [24].

Since the development of SPARK 2014 is currently ongoing, the Muen kernel is implemented using the existing SPARK 2005 language and tools.

#### 2.2Intel x86 Architecture

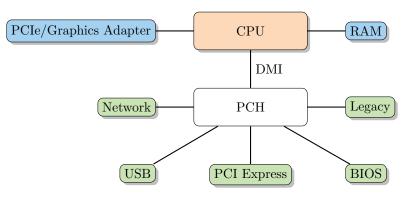

Even though a more detailed familiarity with the subject is required for a full understanding of the design and implementation of the Muen kernel, this section tries to give a short tour of the Intel x86 architecture. The basic components of a modern Intel x86 computer are depicted in figure 2.1. The interested reader is directed to the Intel SDM [17], which contains a complete and in-depth description of the x86 architecture.

#### 2.2.1Processor

The main processor of the system is called the central processing unit (CPU). Multi-processor systems (MP) have multiple CPUs which in turn can have multiple cores. If Intel Hyper-Threading Technology (HTT) is supported, each core has two or more so called *logical CPUs*.

The logical CPUs run processes by executing instructions. These instructions change the state of the logical CPU and the system as a whole.

<sup>&</sup>lt;sup>3</sup>August 2013

Figure 2.1: Intel architecture

#### 2.2.1.1 Execution Environment

A program executing on a processor is given access to resources to store and retrieve information, such as code or data. Resources provided by a modern 64-bit processor constituting the basic execution environment are described in the following list:

Memory address space is used by a program to access RAM.

- **Stack** is located in memory and facilitates subprogram calls and parameter passing in conjunction with stack management resources of the processor.

- **Execution registers** constitute the core of the execution environment. They consist of sixteen general-purpose, six segment and one flag register as well as the instruction pointer.

- **Control registers** define the current processor operating mode and other properties of the execution environment.

- **Descriptor table registers** are used to store the location of memory management and interrupt handling data structures.

- Debug registers allow a program to control and use the debugging functionality of a processor.

- x87 FPU registers offer support for floating-point operations.

- **MMX registers** offer support for single-instruction, multiple-data (SIMD) operations on integer numbers.

- XMM registers offer support for SIMD operations on floating-point numbers<sup>4</sup>.

- Model-specific registers (MSRs) provide control of various hardware and software-related features. Their number and functionality varies depending on the given processor implementation.

- I/O ports provide communication with devices on a different address space.

Further details about the Intel processor execution environment can be found in [17], volume 1, section 3.2.1. All instructions provided by a processor are called an instruction set. The complete Intel instruction set architecture (ISA) is specified in [17], volumes 2A-C.

<sup>&</sup>lt;sup>4</sup>Processors may contain more advanced vector support (e.g. YMM)

#### 2.2.1.2 Caches

The processor has numerous internal caches and buffers of varying sizes and properties. Their main purpose is to increase processor performance by hiding latencies of memory accesses, e.g. reading data from RAM. The most important caches are outlined in the following list:

- Level 1 instruction cache

- Level 1 data cache

- Level 2 & 3 unified caches

- Translation lookaside buffers (TLB)

- Store buffer

- Write Combining buffer

- Branch Prediction Cache (BPC)

Since caches are shared and because they can only be controlled to a limited degree, their state can be changed and observed by different parts of a system. Thus, some of the caches can be used as side-/covert-channels and pose a challenge to effective component isolation.

#### 2.2.1.3 Protected Mode

A modern CPU provides several operating modes of which one is called *protected mode*. In this mode the processor provides different privilege levels also called rings. The rings are numbered from 0 to 3, with ring 0 having the most privileges. Common operating systems use only rings 0 and 3 while disregarding other privilege levels.

Privileged instructions such as switching memory management data structures are only executable in ring 0, also called *supervisor mode*. Operating systems such as Linux usually execute user applications in the unprivileged ring 3, called *user mode*.

#### 2.2.1.4 IA-32e Mode

The Intel 64 architecture runs in a processor mode named *IA-32e*, also known as *long mode*. It has two submodes: compatibility and 64-bit mode. The first submode allows the execution of most 16 and 32-bit applications without re-compilation, by essentially providing the same execution environment as in 32-bit protected mode.

The IA-32e 64-bit submode enables 64-bit kernels and operating systems to run applications making use of the full 64-bit linear address space. The execution environment is extended by additional general purpose registers and most register sizes are extended to 64 bits.

In the context of this project, IA-32e mode generally refers to the 64-bit IA-32e submode if not stated differently. Additional information about this mode of operation and the execution environment can be found in [17], volume 1, section 3.2.1.

#### 2.2.2 Memory Management

Current processors support management of physical memory through means of *segmentation* and *paging*. Application processes running on a processor are provided with a virtual address space. The processes are given the illusion that they run alone on a system and have unrestricted

access to system memory. Memory access of processes are translated using the aforementioned segmentation and paging mechanisms.

Memory management is done in hardware by the memory management unit (MMU). An operating system must set up certain data structures (descriptor tables and page tables) to instruct the MMU how logic and linear memory addresses map to physical memory.

Logical addresses are transformed to linear addresses by adding an offset to the given virtual address. This mechanism is called segmentation. In IA-32e mode, segmentation has effectively been dropped in favor of paging, creating a flat 64-bit linear address space.

Paging is the address translation process of mapping linear to physical addresses. Memory is organized in so called pages. A memory page is the unit used by the MMU to map addresses. IA-32e mode provides different page sizes such as 4 KB, 2 MB and 1 GB.

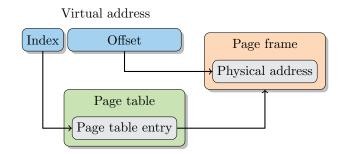

Figure 2.2: One-level address translation

An exemplary one-level address translation process is illustrated in figure 2.2. The MMU splits the linear address in distinct parts which are used as indexes into page tables. A page table entry specifies the address of a physical memory page called *page frame*. Addition of the offset part of the input address to the page frame yields the effective physical address.

Paging structures can be arranged hierarchically by letting page table entries reference other paging structures instead of physical memory pages. In fact, Intel's IA-32e mode uses four levels of address mapping, which are presented in the following list:

- Page map level 4 (PML4) references a page directory pointer table. The address of the currently active PML4 is stored in the CPU's CR3 control register.

- Page directory pointer table (PDPT) references a page directory or a 1 GB page frame.

- Page directory (PD) references a page table or a 2 MB page frame.

- Page table (PT) references a 4 KB page frame.

A linear memory address is split into five parts, when all four levels of paging structures are used. The first element identifies the PML4 entry, the second references the PDPT entry and so on. The fifth part constitutes the offset added to the page frame address. Larger page sizes are supported by letting higher level paging structures reference physical memory pages. In such a case, all remaining parts of the linear memory address are used as offset into the larger page frame.

Additionally, paging structure entries allow to specify properties and permissions such as write access or caching behavior for the referenced physical memory page. The permissions are checked and enforced by the MMU. The paging mechanism enables fine-grained memory management on a per-process basis. The use of different paging structures depending on the currently executing process allows for partitioning and separation of system memory using the MMU. This can be achieved by changing the value of the processor's CR3 register whenever a process switch occurs.

If a process tries to access a memory location that has no valid address translation, the processor raises a page fault exception. The operating system's page fault handler is then in charge to correct the failure condition. It can seamlessly resume the execution of the faulting process after handling the exception. This technique is used by many modern operating systems such as Linux to implement dynamic memory management.

For a more in-depth look at memory management and address translation the reader is referred to [17], volume 3A sections 3 & 4 and [8].

#### 2.2.3 Exceptions and Interrupts

Exceptions and interrupts signal an event which occurred in the system or a processor that needs attention. They can occur at any time and are normally handled by preempting the currently running process and transferring execution to a special *interrupt service routine* (ISR).

Each exception or interrupt has an associated number in the range of 0 to 255, which is called the interrupt vector. Numbers in the range of 0 to 31 are reserved for the Intel architecture. They are used to uniquely identify exceptions, see Intel SDM [17], volume 3A, section 6.15. The remaining vectors can be freely used by hardware devices and the operating system. To avoid vector number clashes hardware interrupts are offset by 32 to move them out of the reserved range. As an example, the hardware interrupt 0 (timer) would be mapped to 32, 1 (keyboard) to 33 and so on. As a result the range of hardware interrupt numbers is restricted to 0 ... 223.

Interrupts are caused by hardware devices to notify the processor that a device needs servicing. An example is a network card that generates an interrupt whenever a data packet is received from the network. The interrupt handler responsible for servicing the network card is invoked upon recognition of the event which then acknowledges further processing of the received data to the device.

Exceptions are generated by the processor itself when it detects an error condition during instruction execution. Causes for exceptions are for example division by zero or page faults.

Interrupts generated by external devices can be blocked by disabling the processor's IF flag in the FLAGS register. When the flag is not set, such interrupts are not recognized by the processor until the flag is enabled again. Exceptions however are not affected by the IF bit and are processed as usual.

The main data structure which facilitates interrupt handling is the *interrupt descriptor table* (IDT). It is a list of entries which point to interrupt handler procedures. The IDT can be located anywhere in system memory and its physical address must be stored in the IDT register (IDTR). When the processor receives an interrupt, it uses the interrupt vector as an index into the IDT to determine the associated handler. Execution control is then transferred by invoking the handler procedure.

#### 2.2.4 Programmable Interrupt Controller

A Programmable Interrupt Controller (PIC) is used to connect several interrupt sources to a CPU. Hardware devices raise interrupts to inform a CPU that some event occurred which must be handled. One of the best known PICs is the Intel 8259A which was part of the original  $PC^5$  introduced in 1981.

$<sup>^5\</sup>mathrm{Personal}$  computer

Early PC/XT ISA systems used one 8259 controller, allowing only eight interrupt input lines. By cascading multiple controllers, more lines can be made available, but a more flexible approach was needed with the advent of multi-processor (MP) systems containing multiple cores. Implementing efficient interrupt routing on an MP system using PICs was problematic.

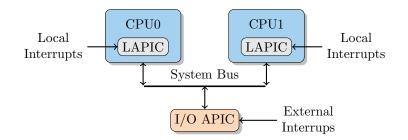

Intel presented the Advanced Programmable Interrupt Controller (APIC) concept with the introduction of the Pentium processor. It was one of several attempts to solve the interrupt routing efficiency problem. The Intel APIC system is composed of two components: a local APIC (LAPIC) in each CPU of the system and the I/O APIC, see figure 2.3 for a schematic view.

Figure 2.3: Local APICs and I/O APIC

A LAPIC receives interrupts from internal sources (such as the timer) and from the I/O APIC or other external interrupt controllers. It sends these interrupts to the processor core for handling. In MP systems, the LAPIC also sends and receives *inter-processor interrupt* messages (IPI) from and to other logical processors on the system bus. Each local APIC has a unique ID called APIC ID. This ID is assigned by system hardware at power up.

The I/O APIC is used to receive external interrupts from the system and its associated devices and relays them to the local APICs. The LAPICs are connected to the I/O APIC via the system bus. The routing of interrupts to the appropriate LAPICs is configured using a redirection table which must be set up by the operating system. For more information about APIC and I/O APIC see Intel SDM [17], volume 3A, chapter 10.

#### 2.2.5 Chipset connectivity

The Intel hardware architecture is constantly evolving. More and more functionality is moved into the CPU to increase performance. With the advent of the Intel 5 Series computing architecture [39], the CPU is directly connected to RAM and some PCI Express (PCIe) devices. The memory controller is integrated straight into the processor, providing fast access to system memory. The memory controller arbitrates RAM access and forwards requests to other resources, e.g. memorymapped devices to the platform controller hub (PCH).

Similarly, the display controller is either fully integrated into the processor or connected via PCIe lanes. The CPU and the PCH are linked via the Direct Media Interface (DMI).

The platform controller hub provides connections to most devices and platform peripherals such as keyboards, network adapters, USB connections and other buses (PCIe etc). It also features the system clock.

#### 2.3 Virtualization

Virtualization is an established architectural concept in computer science and has been in use for decades. Operating systems for example provide virtual address spaces to application processes, giving them the illusion of unlimited, continuous memory. Hence an application does not need to take care of complex memory management tasks and the operating system is able to optimize the usage of physical memory. Another common example is the virtualization of devices such as virtual CD-ROM drives directly using a file-based backend for data I/O [14].

Hardware or platform virtualization is the process of simulating virtual computer hardware that acts like real hardware. The virtualization is performed and controlled by special software, called a *hypervisor* or *virtual machine monitor* (VMM). These two terms are synonyms; for consistency we will use VMM throughout this document. VMMs are classified into two types, as shown in figure 2.4.

Figure 2.4: VMM classification

The VMM runs on the *host* and software that runs in a virtualized environment is called *guest* software. The terms host and guest are generally used to distinguish the software that runs on the physical machine from the software that runs on the virtual machine (VM) [41].

By using virtualization and scheduling techniques, a VMM multiplexes the hardware of a computer making it possible to run multiple guests simultaneously<sup>6</sup> on a single physical machine. This is the most common use-case for virtualization: the consolidation of operating system instances on one server to save power and to improve hardware-resource utilization.

A guest program is separated from the real hardware of a machine. Direct access is restricted and can be controlled by the host VMM. Since the VMM has complete control over the hardware and guest software state, virtualization is also useful for separation purposes. The VMM is able to allow certain communication channels between guest software while restricting others. One guest could have access to the network card, while others share a page in memory but have no access to hardware devices.

The principle idea of virtualization is to run guest code on a (virtual) CPU and only intercept privileged operations accessing resources or system properties for which direct access is prohibited. Various techniques exist to intercept guest instructions, ranging from inspection and modification of the guest software instruction stream (slow) to hardware-assisted virtualization

<sup>&</sup>lt;sup>6</sup>On multicore machines in parallel, on single-core machines in pseudo-parallel

(fast). This thesis focuses on the hardware-assisted approach. The reader is directed to [38] for further information about virtualization mechanisms.

Independent of the chosen mechanism, interception of the running guest leads to a so called *trap* from the guest code into the VMM. The VMM then examines the *exit reason* and reacts accordingly by for example modifying the guest software state and then resuming guest execution.

This method is also used to implement a technique called "trap and emulate". For example, if a guest accesses a device which is emulated by the VMM, a trap into the VMM occurs. The VMM itself or a specialized VM monitor emulates the requested operations of the guest software by directly modifying the state of the virtual processor or memory of the trapping VM.

With hardware-assisted virtualization, traps are handled by the virtualization hardware automatically. The exact behavior is configurable by the VMM software.

#### 2.3.1 Intel Virtualization Technology (VT)

A trap from the guest into the VMM is a costly operation. To reduce traps, modern processors have introduced mechanisms to support the VMM in creating a virtual machine environment. These features not only improve the performance of a virtual machine by avoiding traps, but also greatly simplify the VMM implementation.

Intel Virtualization Technology (VT) provides hardware-assisted virtualization mechanisms for Intel processors. Intel VT encompasses multiple virtualization features:

- Intel VT-x

- Intel EPT

- Intel VT-d

#### 2.3.1.1 Intel VT-x

Intel VT-x provides a virtual machine architecture to allow efficient processor virtualization. An Intel processor reports this feature with the Virtual Machine Extensions (VMX) CPU flag.

The virtual machine architecture is implemented by a new form of processor operation called VMX operation. This mode is enabled by executing the VMXON instruction and provides two operating modes: VMX root operation and VMX non-root operation.

Figure 2.5: Interaction of VMM and Guests

The VMX root operation mode is used by the VMM software while guest software runs in VMX non-root operation mode. A transition from VMX root to VMX non-root is called a VM entry, while a transition from VMX non-root to VMX root is called a VM exit or trap. Figure 2.5 shows the life cycle of a VMM and the transitions between guest software and the VMM.

Processor behavior in VMX root mode is very similar to non-VMX operation. The main difference is the extra instruction set provided by VMX, containing virtualization-specific instructions used to manage VMX processor mode and virtual machine control structures.

In VMX non-root operation however, the execution environment is restricted to facilitate virtualization. Privileged or critical instructions cause VM exits instead of their normal behavior. This allows the VMM to regain control of processor resources and, depending on the trapping instruction, take appropriate action such as emulating certain functionality.

The VMM software initiates a VM entry into guest code by executing the VMLAUNCH and VMRESUME instructions. Only one guest can be active on a logical processor at any given time. The VMM regains control using the VM exit mechanism. If an exit occurs, the VMM analyzes the cause of the exit and acts accordingly. It may resume the guest software or allocate processor time to a different guest. The VMM exits VMX operation by calling the VMXOFF instruction.

The Virtual-Machine Control Structure (VMCS) is used to control VMX non-root operation and VMX transitions. Each virtual machine has an assigned VMCS which allows fine-grained setup of processor behavior in VMX non-root mode. A VMCS contains fields which can be written by the VMWRITE instruction and read via VMREAD in VMX root mode. The fields can be categorized into host-state, guest-state, read-only data and control fields.

On VM entry for example, the state of the host is saved automatically into the subject VMCS by the VMX extensions and restored again on VM exit. On the other hand, the guest-state area is used to save and restore guest state on VM exit and VM entry respectively. The read-only data fields provide VMX status information and the control fields in the VMCS govern VMX non-root operation.

For further information about the VMX processor extensions and VMCS, the reader is directed to the respective section in the Intel SDM [17], volume 3C, chapters 23 and 24.

#### 2.3.1.2 Intel EPT

Extended Page Table (EPT) is Intel's implementation of the Second Level Address Translation (SLAT) virtualization technology. It provides hardware-assisted translation of guest-physical memory addresses to host-physical addresses. Guest-physical addresses are translated by traversing a set of EPT paging structures provided by the VMM to produce physical addresses that are used to access memory.

The EPT paging structure confines the host-physical memory region that a guest virtual machine is allowed to access, thereby making it possible to safely run unmodified guest OS memory management code. Access to host-physical memory outside of the allowed region results in an EPT violation trap.

Without EPT, the burden of translating guest-physical addresses to host-physical addresses while guaranteeing guest/vmm and guest/guest memory space separation rests with the VMM. This is a non-trivial task which is highly inefficient. EPT removes the complexity of manual memory address translations via shadow page tables from the VMM, making the code simpler while improving virtualization speed. For more information about EPT see Intel SDM [17], volume 3C, section 28.2.

#### 2.3.1.3 Intel VT-d

Virtualization Technology for Directed I/O (VT-d) provides hardware support for I/O-device virtualization. While VT-x provides the support to virtualize the platform (i.e. the processor), VT-d is used to simplify the direct assignment of devices to virtual machines by providing direct memory access (DMA) and device interrupt remapping functionality. VT-d provides an I/O memory management unit (IOMMU) required to control device DMA.

The IOMMU implements address translation functionality similar to the MMU, but for accesses to system memory initiated by I/O devices. This is necessary since PCI devices can perform DMA which bypasses the processor's MMU memory protection. Like the MMU, an operating system must initialize data structures and set up the IOMMU for proper separation of physical memory accessible by devices.

The VT-d technology is outside the scope of this master thesis, the reader is directed to [16] for a more in-depth discussion.

#### 2.4 Separation Kernel

In a system with high requirements on security, functions needed to guarantee these requirements must be isolated from the rest of the system and are called the Trusted Computing Base (TCB). To be trusted, this code must be kept sufficiently small and straightforward to allow formal verification of code correctness. Lampson et al. [19] define the TCB of a computer system as:

A small amount of software and hardware that security depends on and that we distinguish from a much larger amount that can misbehave without affecting security.

Code that is part of the TCB is called *trusted* while components that have no relevance to the guarantee of security properties are called *untrusted*.

A separation kernel (SK) can be seen as the fundamental part of a component-based system since its main purpose is to enforce the separation of all software components while reducing the size of the TCB. The concept of separation kernels was introduced by John Rushby in a paper published in 1981 [31]:

The task of a separation kernel is to create an environment which is indistinguishable from that provided by a physically distributed system: it must appear as if each regime is a separate, isolated machine and that information can only flow from one machine to another along known external communication lines.

The separation kernel must therefore guarantee that the components can only interact according to a well-defined policy while running on the same physical hardware.

A system policy dictates the partitioning of hardware resources like CPU, memory or assignment of devices to components. The kernel guarantees this isolation by emulating a suitable runtime environment for each component, creating the impression of multiple (virtual) machines. By using modern virtualization techniques, the kernel is able to delegate certain management tasks to the hardware. This allows the separation kernel code to be relatively simple, which is a precondition for formal verification of software.

Because of the simplicity requirement, a system running on top of a separation kernel is relatively static. The system policy is compiled to a suitable format at system integration time and cannot change during runtime. This is also the main difference between the separation kernel concept and other forms of microkernels which provide hardware abstraction layers, advanced mechanisms for inter-process communication (IPC) and dynamic resource management. A separation kernel does not implement such functionality; its sole purpose is to guarantee component separation according to a policy while maintaining a small TCB in terms of size as well as complexity. Policy authors must make sure that the system specification is sound and that only intended communication channels are specified between components. Of course, this task can be simplified and aided by applying appropriate support tools.

#### 2.4.1 Subjects

The separation kernel isolates parts of the TCB into multiple components interacting via welldefined interfaces. In this paper, such components are called *subjects*.

As previously mentioned, only these features necessary to guarantee subject separation are present in a separation kernel. Advanced features required to isolate and virtualize a complex subject are implemented as dedicated non-privileged subjects, so called *subject monitors* (SM). A complex subject could be a complete operating system like Linux.

To allow more runtime flexibility, a separation kernel could also employ a dedicated subject to offload management tasks. Such a subject runs in normal unprivileged mode but is allowed to interact with the SK over a specialized interface.

#### 2.4.1.1 Trust

In the larger context of a component-based system, some subjects can be considered to be part of the TCB and must therefore be trusted to operate according to their specification. Such subjects must be developed with the same diligence as the separation kernel itself.

As an example: a subject is in charge of data encryption and passes the encrypted data to a second subject which provides network connectivity. A security property could be that information must always be encrypted when transmitted over the Internet. To achieve this, the encryption subject must ensure that no unencrypted information flows to the network subject. Thus the encryption subject must be considered part of the TCB and is called a *trusted* subject since its failure would break the security guarantee.

On the other hand, the network subject is not security critical as long as the encryption subject works according to its specification. It is therefore not part of the TCB, which means it is an *untrusted* subject.

#### 2.5 Motivation

As stated in the previous section, software must be simple in order to establish trust in the correct functioning of the code, either through manual review or formal verification. Even though the tools to automate formal verification are progressing fast, the constraints on the software to be verified are still severe. If the SLOC<sup>7</sup> count and thus complexity of a software project exceeds a critical threshold<sup>8</sup>, it is no longer possible to automatically prove integrity and security requirements or to perform a manual review, because the required effort is just too big.

This is the reason why common operating system kernels are not suitable for use as a foundation for high assurance systems that employ a small TCB. The Linux kernel currently has over 14 million lines of code. While functionality can be loaded as modules, Linux is still a monolithic kernel at the architectural level, with the complete code running in the same address space and privilege level. A programming error in a device driver for example could compromise the integrity of the entire system.

The motivation for this project is to provide a freely-available SK with a permissive licensing model to allow reviews and modification of the source code and design documents. It should be possible to independently reproduce verification artifacts such as automated proofs. In the eyes of the authors, this approach should ultimately result in a separation kernel that is applicable to environments where high integrity and security is demanded.

$<sup>^7\</sup>mathrm{Source}$  lines of code

<sup>&</sup>lt;sup>8</sup>The threshold depends on the programming language and support tools

There have been many recent advances in hardware support for virtualization that greatly simplify the design and implementation of a security kernel. The authors believe that now is the perfect time to launch a separation kernel project which benefits from these hardware capabilities.

#### 2.6 Goals

The main goal of this project is to implement a freely-available, open-source separation kernel. The kernel sources will be licensed under the GNU General Public License (GPL) [11].

SPARK is chosen as the main implementation language since this guarantees the availability of advanced and approved tools to write high assurance code. The SPARK tools will be utilized to show certain properties of the kernel code, especially proof of absence of runtime errors is desired. The code of the kernel must also be as small as reasonable to facilitate a lean TCB.

Operations not strictly required in the kernel should be implemented in a special trusted subject written in SPARK. This subject is called  $\tau 0$  and is considered an integral part of the Muen TCB. While keeping the kernel as simple as possible, this will allow for later adoption of more dynamic resource handling and scheduling mechanisms.

The target platform of the SK is 64-bit Intel. No abstraction layer will be provided to support other processor architectures. Instead, the kernel shall leverage the latest hardware features of the Intel platform to implement the isolation while maintaining a small code base.

The main task of the SK is to separate subjects. This is why it must only allow intended data flows according to the policy and it should prevent or limit possible side- or covert-channels.

#### 2.7 Related Work

This section presents related projects. While they share many similarities, the main difference is that the Muen kernel aims to combine various approaches: use of advanced Intel hardware virtualization features, Intel x86 64-bit target platform, small code size, application of verification and proof techniques and making the source code and documentation freely available.

#### 2.7.1 seL4

seL4 is a microkernel of the L4 [20] family which has been formally verified [18]. It aims to provide high assurance of functional correctness by means of machine-checked formal proofs. Using the theorem prover Isabelle/HOL [27], it has been shown that the C implementation correctly implements an abstract specification.

To our knowledge seL4 is the most advanced project in the field of formal verification combined with operating system research. Unfortunately its availability and use is rather limited by restrictive licensing. While parts of the seL4 project are available for non-commercial use, the source code of the kernel has not been published. Thus it is not possible to reproduce the formal proofs.

#### 2.7.2 XtratuM

XtratuM is a type 1 hypervisor specially designed for real-time embedded systems [22]. It is developed by the Real-Time Systems group of the Polytechnic University of Valencia. It uses para-virtualization to provide one or more virtual execution environments for partitions. This means software running as partitions must be modified accordingly to run on top of XtratuM. The processor privilege mechanism (supervisor and user mode) is used to separate the VMM from partitions.

The whole project is open-source and published under the GPL license. It is implemented in C and Assembly. While it supports various platforms such as LEON2/3 (PowerPC) and Intel x86, it does not support IA-32e mode.

#### 2.7.3 NOVA

NOVA is a recursive acronym and stands for NOVA OS Virtualization Architecture [34]. It applies microkernel construction principles to create a virtualization environment. Its authors have coined the term microhypervisor which is short for microkernelized hypervisor.

NOVA has been developed from scratch with the goal to achieve a thin hypervisor layer, a user-level virtual-machine monitor and additional unprivileged components to reduce the attack surface on the most privileged code and thus increase the overall system security. It runs on Intel and AMD x86 processors with support for hardware virtualization and is implemented in the C++ programming language. The source code is publicly available [33] and has been released under the GPL open-source license.

While NOVA is a very promising architecture it is not a SK and provides insufficient temporal isolation. The choice of programming language (C++) and its dynamic nature (in general a very desirable property) increases the verification complexity to the point where it might be infeasible.

#### 2.7.4 Commercial Separation Kernels

There are several commercial offerings for separation kernels by various vendors:

- INTEGRITY-178B by Green Hills Software, Inc. is a separation kernel EAL-6+ certified against the separation kernel protection profile [26].

- PikeOS by SYSGO AG is a microkernel-based real-time OS.

- LynxSecure by LynuxWorks Inc. is a type 1 embedded hypervisor for the Intel x86 architecture.

- VxWorks MILS Platform by WindRiver Inc. is a type 1 hypervisor-based, SKPP-conformant MILS separation kernel.

- PolyXene by Bertin Technologies, is a microkernel-based hypervisor EAL-5 certified against the Guest Operating System Hosting Framework protection profile.

None of these companies publish detailed technical documentation or provide access to source code. Thus there is not enough information available for a thorough technical analysis to assess the assurance provided by these kernels (e.g. if the kernels are suitable for formal verification and what kind of verification has been performed). Simply put, there is not enough information to verify the high robustness claims made by the vendors.

### Chapter 3

## Design

The design of the Muen kernel is based on the concept described in [7] and inspired by the Common Criteria separation kernel protection profile (SKPP) [26]. The protection profile has been used in the certification of Green Hills' INTEGRITY-178B kernel and has been retired by the National Information Assurance Partnership (NIAP) in 2011. Nevertheless we believe the document can serve as a sound basis and provide guidance to derive requirements for a separation kernel appropriate for systems requiring high robustness.

The separation kernel should allow the construction of systems that could be exposed to attackers with high potential and deployed in the most difficult threat environments.

The first part of the chapter presents what is considered out of scope in the context of this project. It is followed by the requirements that are at the core of the kernel design. After that the subject concept is introduced, which is in turn needed for the presentation of the overall system architecture and the design of the Muen kernel in section 3.4.

#### 3.1 Scope

The focus of this project is to design and implement a separation kernel, that guarantees strong separation between subjects and can thus serve as a basis for a component-based system. This section describes the issues that are considered out of scope but mentioned nevertheless for the sake of completeness.

It is assumed that all untrusted subjects can potentially be subverted. The kernel is solely concerned with the correct enforcement of a given system policy, by only allowing intended information flows between subjects and arbitrating resource access.

The following issues, while very important in the context of constructing a high assurance system, are considered outside the scope of this thesis:

- **System initialization** The kernel starts executing after the bootloader hands over execution. It is assumed that the system is set up and initialized properly. How the system is securely bootstrapped (e.g. using a trusted boot process) and initialized and how the integrity of the kernel is assured is not considered.

- **Hardware** It is assumed that hardware, such as the CPU, memory management unit and other devices, are working correctly according to their specification. Problems due to buggy or even malicious hardware are out of scope.

- **Physical attacks** Issues predicated on an attacker having physical access to the system are not considered.

- **Firmware** A modern PC contains firmware and many embedded controllers that are only partly (if at all) controllable by an operating system kernel. This includes technologies such as Intel AMT/ME, System Management Mode (SMM) and the system BIOS<sup>1</sup>, which have access to sensitive system resources.

- **Policy validity** The separation kernel provides the mechanisms to enforce a user-defined policy. The focus is on the correct enforcement of a provided system configuration. The user is in charge of assuring the correctness and consistency of the overall system policy.

- **Communication** The separation kernel must provide a mechanism to establish directed communication channels between subjects. It is however not the duty of the kernel to provide a communication abstraction such as message passing or a remote procedure call (RPC) interface.

**Recovery** How a system can be restored to a secure state after a compromise is out of scope.

These points must be considered and addressed when building a high assurance system based on the separation kernel architecture.

#### 3.2 Requirements

The following properties specify the requirements of the separation kernel and the system's TCB:

- 1. The kernel implementation shall be sufficiently small and robust to allow thorough review and verification.

- 2. System resources internal to the kernel, that are not exported to subjects, shall not be accessible.

- 3. The kernel shall provide mechanisms to enforce a given policy and not perform autonomous policy decisions.

- 4. The kernel shall support the Intel IA-32e/64-bit architecture and system memory larger than 4GB.

- 5. The kernel shall allow the implementation of small and simple components and not impose unnecessary restrictions that would increase subject complexity.

- 6. A subject shall be able to only use its assigned resources. Access to other resources shall be prohibited. This includes devices and memory that has not been allocated to any subject.

- 7. Assignment of subject resources shall be static. A malicious subject shall not be able to gain access to additional resources or consume all system resources.

- 8. Isolated subjects shall not be able to exchange any information.

- 9. Information flows between subjects shall only be present if explicitly specified in the system policy.

<sup>&</sup>lt;sup>1</sup>Basic Input/Output System

- 10. It shall be possible to specify directed information flows, where data can be transferred from source to destination but not in the reverse direction.

- 11. 64-bit programs shall be supported to run as subjects.

- 12. Subjects shall be able to use hardware devices and process device generated interrupts.

- 13. A mechanism for inter-subject notifications shall exist.

- 14. The Muen kernel design, source code and documentation shall be made freely available to allow independent verification and analysis.

# 3.3 Subject

A subject is a software component executed by the separation kernel. Similar terms used in literature are partition, container, task or component. Subjects constitute the majority of a system based on the Muen kernel. They are intended to be used as the building blocks of a component-based security system.

The main purpose of the kernel is to execute an arbitrary number of subjects, giving them access to assigned resources and only allowing communication between subjects via explicitly defined channels. The kernel manages subject execution and treats all subjects equally.

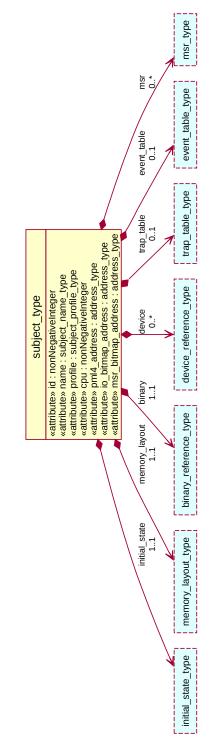

Information related to a subject is divided into two distinct categories:

- **Specification** encompasses all static configuration data, that is constant and does not change during the runtime of the system, e.g. assigned hardware devices and memory resources.

- **State** is made up of all transient values that are potentially modified by the execution of a subject, e.g. CPU register values.

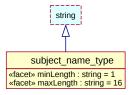

# 3.3.1 Subject Specification

The specification defines the resources that a subject is allowed to access, what execution environment the kernel must provide for the subject, the initial state and of course the subject binary itself. All resources that a subject can access, must be explicitly defined in the specification, which includes the complete memory layout of the subject.

This information is part of the overall system specification and is fixed at integration time. It does not change during the execution of the system. The kernel keeps this information as part of the compiled system policy in read-only memory. Since subjects are unable to access kernel memory, the subject specifications cannot be tampered with.

#### 3.3.2 Subject State

Running a subject inevitably affects and changes the execution environment. The state of a subject encompasses all system elements that are visible to the subject. In particular this includes the CPU registers, instruction and stack pointer as well as control register values.

Since the kernel suspends and resumes subject execution and potentially multiple subjects can be executed in arbitrary order, the state of the system as viewed by the subject must be saved. The state must be restored accurately upon resumption, otherwise the subject will not be able to execute seamlessly.

Subject management information used by the kernel during runtime is also considered part of the subject state. This includes a data structure for storing pending interrupts to be delivered to the subject.

# 3.3.3 Subject Profile

Two types of subjects are distinguished:

- Native applications

- Virtual Machine (VM) subjects

Each of these types is captured by so called *subject profiles*. These profiles determine the execution environment and architectural features (e.g. memory management) that the subject is allowed to use. Profiles are declared in the subject specification. The currently supported profiles are described in the following sections.

#### 3.3.3.1 Native Subject

A *native* subject is a 64-bit application, that executes directly on the virtual processor without any supporting operating system kernel or runtime environment. Such applications are also known as bare bones, bare metal or bare machine.

The execution environment of the native subject profile has the following main properties:

- IA-32e/64-bit processor mode

- No mode switching

- No memory management (static paging structures)

- No hardware exception handling

- No control register access

#### 3.3.3.2 VM Subject

A virtual machine (VM) subject has more control over its execution environment. The VM profile is intended for executing operating systems such as Linux.

The execution environment of the VM subject profile has the following main properties:

- Switching between 32-bit and 64-bit modes

- Memory management and page table management via EPT

- Hardware exception handling

- Restricted control register access

# **3.4** Architecture

The core mechanism used to separate subjects is Intel's hardware-assisted virtualization technology VT-x. The kernel executes in VMX root mode, while subjects run in VMX non-root mode. This shields the kernel from access by subjects. Figure 3.1 illustrates the basic system architecture: the Muen kernel executes two isolated subjects that have no access to any kernel resources. The native subject is a bare bones application and the second subject is a virtual machine (VM) type subject, e.g. an operating system.

Figure 3.1: Architecture overview

Resource assignment to subjects is static and done prior to the execution of the system. All available resources provided by a platform running the Muen kernel must be specified in a system policy. Similarly, scheduling plans and all subjects running on the system are part of the policy.

This relieves the kernel from dynamic resource management and avoids the associated complexity, which greatly simplifies the kernel design and in turn its implementation.

The policy is described in detail in section 3.4.2.

# 3.4.1 Subject Execution

The kernel initializes the subject execution environment and state according to the subject specification. The execution is started from the subject entry point and continues for a predefined period of time. Once the time has passed, a trap into the kernel occurs and the current state of the subject is saved for later resumption.

A subject is constrained to the environment specified by the subject profile and the resources assigned to it by the policy. If a subject performs an illegal resource access or an operation not allowed by the profile, a trap occurs and the kernel is invoked. The kernel can then determine the cause for the transition and handle the condition according to policy.

#### 3.4.1.1 Subject Monitor

When a subject tries to access resources such as devices that are emulated, a system component must perform the necessary actions and change the subject's system state accordingly. This is to give the subject the impression that it has unrestricted access to a device while in reality the necessary operations are effectively emulated by another component.

In a system based on the Muen kernel, this monitoring function can be implemented by a subject termed subject monitor. Such a monitoring subject can be given access to the state of another subject, effectively allowing it to change the system state of the monitored subject. A so called *trap table*, which is part of the subject specification, allows to specify that execution should be handed over to a subject monitor when a trap occurs.

Historically this monitoring function has been implemented as part of the VMM of the virtualization system. Since emulation operations can be very involved and quickly grow in complexity, it is very desirable to extract this functionality from the separation kernel and thus from the TCB. Since subjects are confined by the separation kernel the subject monitor concept achieves this property. This approach has been pioneered by NOVA, see [34].

# 3.4.2 Policy

To best fulfill the requirements, a system using the Muen kernel uses static resource assignment and system specification. The main idea is to have a complete description of the system including all resources such as system memory, devices and subjects in the form of a policy. The defined resources can be assigned to subjects. Since the resources and subjects are fixed at integration time, the policy can be analyzed and validated prior to execution.

The following list encompasses the system policy:

- Hardware resources

- Kernel specification

- Subject specifications

- Scheduling information

#### 3.4.2.1 Memory

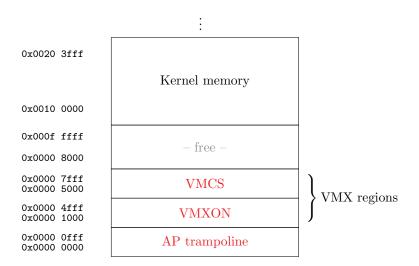

All memory resources of a system are static and explicitly specified in the system policy. Apart from a few special memory regions, such as the application processor trampoline (see section 4.4.1), there are no implicitly allocated data structures. This allows one to determine the exact memory layout of the final system at integration time.

The kernel and each subject specifies its memory layout. The memory layout defines which physical memory ranges are accessible, their location in the virtual address space of the binary and additional attributes. These attributes define read/write and executable properties of the memory region and the caching behavior.

Since the layout is controlled by memory management data structures, each subject has its own distinct set of page tables. To assure that a subject cannot alter the memory layout, it must not have access to any page tables, including its own. This is achieved by not mapping memory management structures into the address space of any subject.

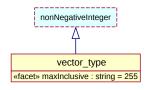

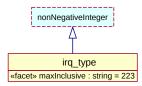

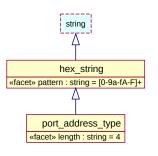

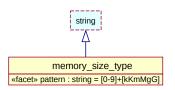

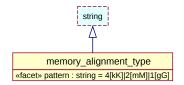

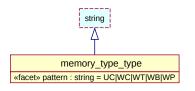

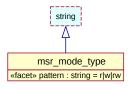

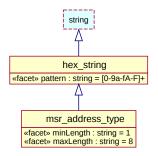

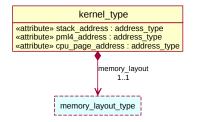

Figure 3.2 illustrates the physical memory structure of an example system. The hexadecimal values on the left side are physical addresses in memory.